- WHATS MODELSIM PE STAND FOR FULL

- WHATS MODELSIM PE STAND FOR SOFTWARE

- WHATS MODELSIM PE STAND FOR CODE

- WHATS MODELSIM PE STAND FOR PLUS

WHATS MODELSIM PE STAND FOR FULL

Scenario: Creating a RAM or a FIFO that does not uses the full width of the RAM block in the Silicon Symptoms: During the compile stage, Designer outputs warning messages informing you that there are ports floati KI17107: Floating Port Warning When Using RAM in Axcelerator Symptoms: On certain PCs, customers sometimes get the “Server Busy” dialog-box when Scenario: Trying to open new or existing Schematic in Libero displays the “Server Busy” message. KI14442: Invoking Viewdraw – “Server Busy” message

Symptoms: The Silicon Sculptor II does not communicate with c

WHATS MODELSIM PE STAND FOR SOFTWARE

Scenario: After hooking up Silicon Sculptor and turning on the Silicon Sculptor II hardware, invoke Silicon Sculptor software (any software version). KI51915: Silicon Sculptor II Communication Error with Windows 2000 Platform

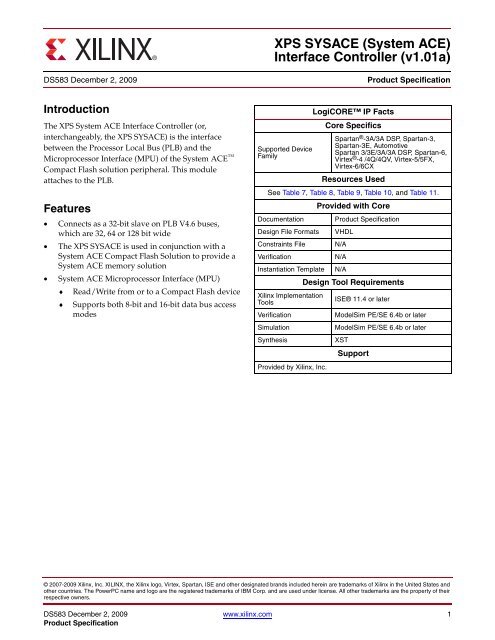

Scenario: adapter: SM208PQ-ACTEL-2 Symptoms: The Silcon Sculptor v4.37 Self-Test fails with error messages similar to the following : Unit Number: 1CPU/RAM/ROM/LOGIC PASSEDCOMMUNICATIONS PASSEDPOWER SUPPLI KI50900: Inconsistencies of Self Test Results in Different Sculptor Windows Versions Symptoms: While running self-test, the customer gets one of the Scenario: Was using FlashPro software v1.0/1.1, just installed newer FlashPro software, trying to run self-test before running the software itself. KI48255: Running Self-Test with newer FlashPro Software Versions gives an Error Some pins may not read or drive themselves correctly. Scenario: While using the APA150-PQ208 BSDL file in boundary scan testing Symptoms: Interconnectivity test will fail if this BSDL file is used. KI47453: Incorrect APA150-PQ208 BSDL file Symptoms: When executing the PROGRAM operation, the programming software returns an ‘External Voltag Scenario: Programming multiple APA Devices using FlashPro, when Vddp is supplied from the Target System. KI45690: Failure to Program multiple APA devices in a Chain Scenario: When performing post-layout simulation in Modelsim and looking at internal signals, what is the difference between the “d” and “d_ipd” signal? Also the “clk” and “clk_ipd” s KI44946: Viewing simulation waveform signals (*_ipd signals) However, this is not true with clock skew.

WHATS MODELSIM PE STAND FOR PLUS

Symptoms: Clock frequency should be the inverse of reg-reg delay plus setup time. Scenario: Frequency doesn’t match with reg-reg delay.

KI44010: Explanation of the Timer Expanded Path Scenario: Some Silicon Sculptor II can not program any anti fuse devices except Act1 and 40MX devices Symptoms: Programmer passes the self-test but during blank check operation it says, “Device is not blank KI40715: FineICC test failure in Silicon Sculptor II However, these signals are defined in pre-synthesis simulation. Scenario: When performing post-synthesis and post-layout simulation in ModelSim, customers observe ‘unknown’ signals in their design. KI37475: ‘Unknown’ signals in post-synthesis and post-layout simulation Scenario: Running Libero IDE / Designer software with Windows XP SP2 Symptoms: The MEM_BAD_POINTER error message appears (from the SmartHeap Library used by Libero IDE and Designer software).Figure 1. If I setup the exact same project in ISE 14.KI41062: Using Libero IDE or Designer with Windows XP SP2 The issue is that the 'Wave window' of ModelSim shows all the signals as either hi-Z or don't care 'X': I had to use ISE 10.1 and ModelSim SE 5.7 because the more recent versions of the ISE don't support any of the Spartan devices any more, IIUC (let alone Vivado). Wait 100 ns for global reset to finish

WHATS MODELSIM PE STAND FOR CODE

While getting my feet wet with an old Spartan2-Board I tried to setup a 1-bit full adder with the Verilog code and accompanying testbench as below: module full_adder(s, cout, a, b, cin)

0 kommentar(er)

0 kommentar(er)